|

服务说明

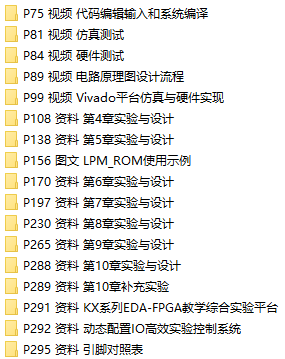

Verilog版 本书系统地介绍了EDA技术和Verilog HDL硬件描述语言,将Verilog HDL的基础知识、编程技巧和实用方法与实际工程开发技术在Quartus II /Vivado上很好地结合起来,使读者通过本书的学习能迅速了解并掌握EDA技术的基本理论和工程开发实用技术,为后续的深入学习和发展打下坚实的理论与实践基础。 作者依据高校课堂教学和实验操作的规律与要求,并以提高学生的实际工程设计能力和自主创新能力为目的,合理编排全书内容。全书共分为6个部分:EDA技术的概述、Verilog HDL语法知识及其实用技术、(Quartus II/Vivado工具应用)及IP核的详细使用方法、有限状态机设计技术、16/32位实用CPU设计技术、Verilog仿真与Test Bench编写方法,除个别章节外,大多数章都安排了相应的习题和大量针对性强的实验与设计项目。书中列举的Verilog HDL示例都经编译通过或经硬件测试通过。 本书主要面向高等院校本、专科的EDA技术和Verilog HDL语言基础课,推荐作为电子工程、通信、工业自动化、计算机应用技术、电子对抗、仪器仪表、人工智能等学科专业和相关实验指导课的教材用书或主要参考书,同时也可作为电子设计竞赛、FPGA开发应用的自学参考书。 VHDL版 本书系统地介绍了EDA技术和VHDL硬件描述语言,将VHDL的基础知识、编程技巧和实用方法与实际工程开发技术在Quartus II /Vivado上很好地结合起来,使读者通过本书的学习能迅速了解并掌握EDA技术的基本理论和工程开发实用技术,为后续的深入学习和发展打下坚实的理论与实践基础。 依据高校课堂教学和实验操作的规律与要求,并以提高学生的实际工程设计能力和自主创新能力为目的,合理编排全书内容。全书共分为7个部分:EDA技术的概述、VHDL语法知识及其实用技术、Quartus II/Vivado及IP核的详细使用方法、有限状态机设计技术、16/32位实用CPU设计技术及创新实践项目、基于基于ModelSim的Test Bench仿真技术、基于MATLAB和DSP Builder平台的EDA设计技术及大量实用系统设计示例。除个别章节外,大多数章都安排了相应的习题和大量针对性强的实验与设计项目。书中列举的VHDL示例都经编译通过或经硬件测试通过。 本书主要面向高等院校本、专科的EDA技术和VHDL语言基础课,推荐作为电子工程、通信、工业自动化、计算机应用技术、电子对抗、仪器仪表、人工智能等学科专业和相关实验指导课的教材用书或主要参考书,同时也可作为电子设计竞赛、FPGA开发应用的自学参考书。 可直接扫码下载资料

可扫码申请样书

|